PCを組み立てたりアップグレードしたりする際、多くの人はGPU、CPU、SSDに注目します。しかし、PCI Express(PCIe)レーンがこれらのパーツをつなぐ目に見えない高速道路であることに気づいている人はほとんどいません。PCIeレーンは、GPUとCPUの通信速度、ボトルネックなしで使用できるNVMe SSDの数、そして次回のアップグレードが期待通りのパフォーマンスを発揮するかどうかを左右します。

この記事では、PCIe レーンとは何か、どのように機能するか、PCIe Gen4 と Gen5 の新機能、システムを計画する際によりスマートな選択を行う方法について説明します。

PCIe レーンとは何ですか?

PCIe レーンは、PCI Express インターフェースの基本的な通信チャネルです。

各レーンには 2 組のワイヤ (1 組はデータ送信用、もう 1 組は受信用) が組み込まれており、PCIe は全二重 (データは同時に両方向に流れる) になります。

複数のレーンをグループ化して、より広い接続を作成することができます。これは、多くの場合、×1、×4、×8、または×16 というラベルで表示されます。

×1: Wi-Fi やキャプチャ カードなどの小型アドイン カードに適しています。

×4: NVMe SSD および M.2 スロットで使用されます。

×16: 最大帯域幅を実現する GPU 専用。

つまり、レーン数が増えると帯域幅も増えます。

PCIe レーンの詳細については、 以前の記事で詳しく説明しています。

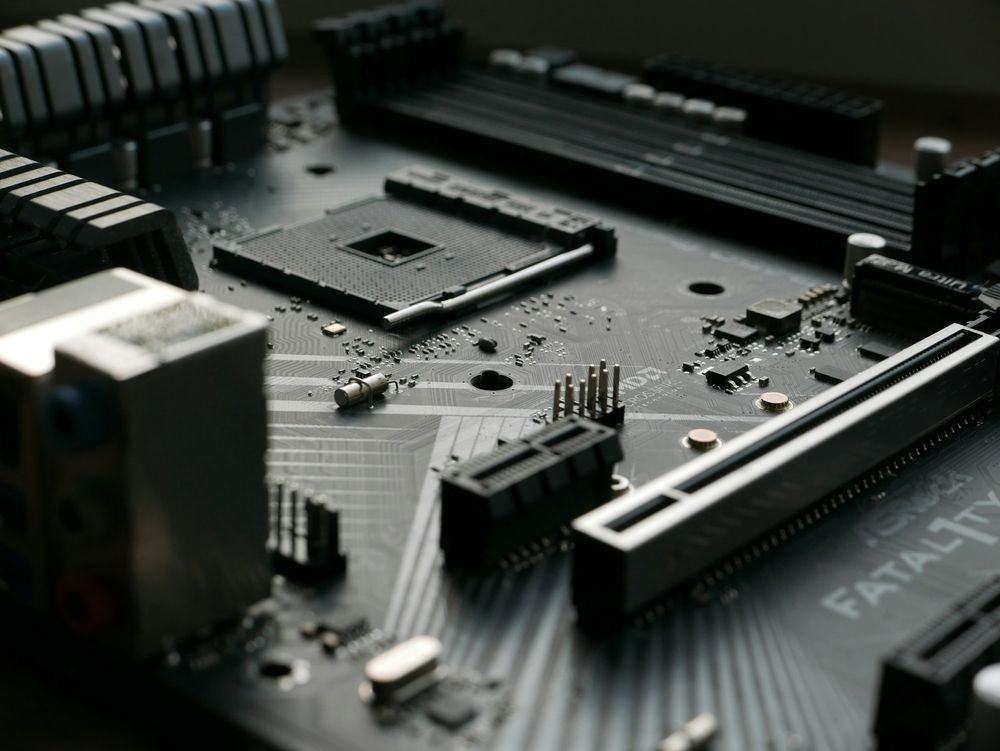

CPUサポートレーンとチップセットレーン

すべての PCIe レーンが同じように作成されるわけではありません。

最新のシステムには、2 つの PCIe レーン ソースがあります。

CPUレーン:プロセッサに直接接続されます。レイテンシが最も低く、帯域幅が最も広くなります。

チップセット (PCH) レーン: マザーボードのチップセットを経由してルーティングされ、リンク (Intel では DMI、AMD では Infinity Fabric と呼ばれます) を使用して CPU に接続されます。

チップセット レーンでは単一の DMI リンクが共有されるため、NVMe SSD やキャプチャ カードなどの複数の高速デバイスが帯域幅を競合すると、ボトルネックになる可能性があります。

たとえば、一般的な AMD Ryzen または Intel Core CPU は、通常次のように割り当てられる 16~20 の直接レーンを提供します。

GPU用16レーン(x16スロット)

メインNVMe SSD用の4レーン

残りはチップセットリンクに使用される

その他すべて (USB コントローラー、SATA ポート、Wi-Fi モジュール) は、チップセットの低速レーンを介して接続されます。

PCIeの世代と速度

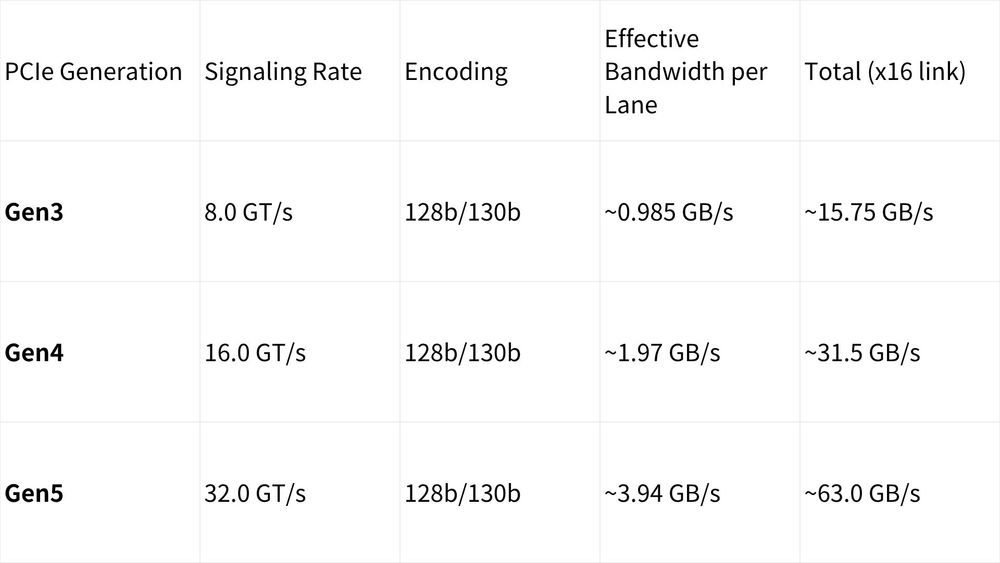

新しい PCIe 世代ごとに、レーンあたりのデータ レートが以前の世代と比べて 2 倍になります。

数字を見てみましょう:

(GT/s = 1秒あたりのギガ転送数)

簡単に言うと:

PCIe Gen4 ×8 スロットは Gen3 ×16 スロットとほぼ同じ速度です。

Gen5 ×8 スロットはすでに Gen4 ×16 の速度を超えており、より少ないレーン数でも膨大なスループットを実現できます。

そのため、最新の GPU と SSD では、割り当てられたレーン数が少なくても驚異的なパフォーマンスを実現できます。

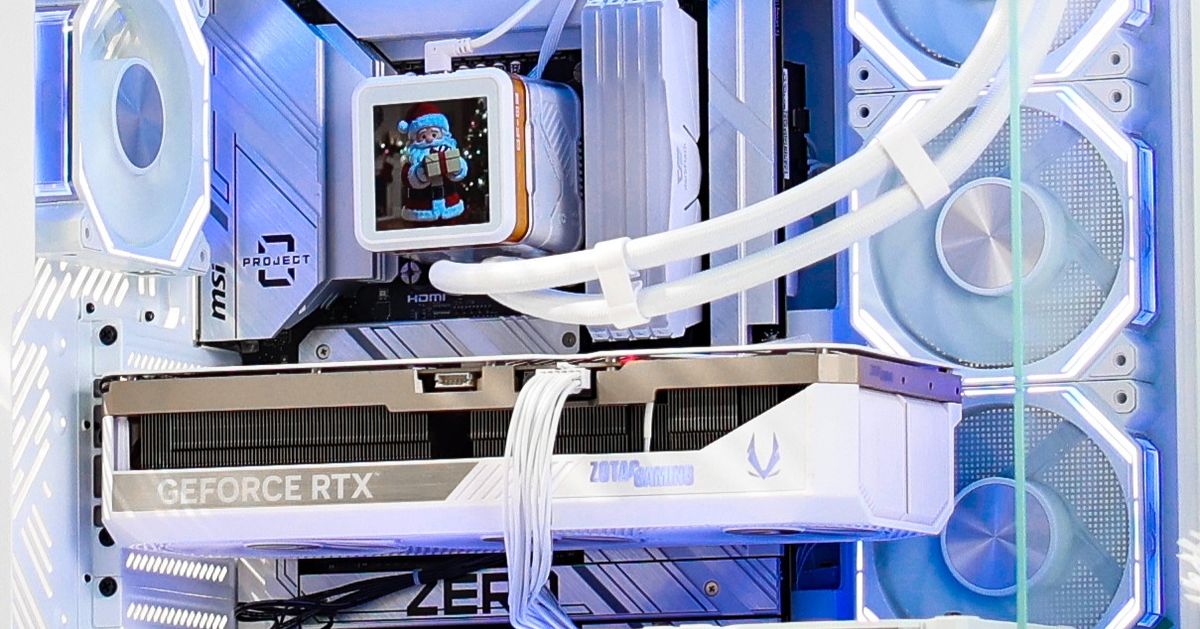

PCIe Gen4 vs Gen5: エンジニアリングの飛躍

PCIe Gen5は単に「2倍の速度」というだけではありません。設計もはるかに難しくなります。

32GT/sでは、信号損失が1ビットたりとも問題となります。マザーボードメーカーは以下を使用する必要があります。

高品質PCB材料(低損失ラミネート)

より短いトレース長

信号の整合性を維持するためのリドライバまたはリタイマー

ルーティング中の正確なインピーダンス制御

Gen5 マザーボードがより高価なのはそのためです。データ エラーを発生させずにこれらの速度を処理するには、高度なエンジニアリングが必要です。

PC ビルダーにとって、重要なポイントは次のとおりです。

超高帯域幅のワークロード(3Dレンダリング、AIトレーニング、マルチNVMe RAIDなど)を駆使しない限り、日常的なタスクでGen5のスピードを「体感」することはないでしょう。しかし、将来性への配慮というメリットは確実に得られます。

実世界の例: 現代のCPUにおけるレーン割り当て

最新の Intel または AMD CPU を使用した一般的なセットアップを視覚化してみましょう。

[CPU]

│

├── PCIe x16 → GPU

§── PCIe x4 → NVMe SSD (M.2スロット)

└── PCIe x4 → チップセットリンク(DMI / ファブリック)

│

├── USBポート

├── SATAドライブ

├── セカンダリNVMeスロット

└── ネットワーク / Wi-Fi カード

2台目のNVMeドライブを取り付けると、マザーボードがレーンを共有または分割することがあります。これにより、GPUの帯域幅が×16から×8に減少する場合があります。これは通常、ゲームパフォーマンスに大きな影響はありませんが(Gen4 ×8 = Gen3 ×16)、マザーボードのマニュアルでどのスロットが帯域幅を共有しているかを確認することが重要です。

PCIeレーンが重要な理由

超高速コンポーネントを使用していても、チップセットに過負荷をかけたり、CPU レーンを非効率的に分割したりすると、帯域幅のボトルネックが発生する可能性があります。

レーン管理がパフォーマンスに与える影響は次のとおりです。

GPU 帯域幅: レンダリングおよび計算タスクにとって重要です。

ストレージ帯域幅: 特に RAID において、NVMe SSD の転送速度に影響します。

アドイン カード: キャプチャ カード、NIC、アクセラレータにより、チップセット レーンが簡単に飽和状態になる可能性があります。

CPU レーンを効率的に使用することで、各デバイスにプロセッサへの明確で高速なパスが確保されます。

そのため、AMD Threadripper や Intel Xeon などのハイエンド プラットフォームでは、マルチ GPU やワークステーションのセットアップに最適な 48 ~ 128 レーンを提供しています。

将来の展望: PCIe Gen6以降

次のステップである PCIe Gen6 では、PAM4 (パルス振幅変調) 信号を使用してレーンあたり 64 GT/s に速度がさらに 2 倍になります。これは、信号の送信方法に大きな変化をもたらします。

しかし、これにより、さらに大きな設計上の課題が生じます。

消費電力の増加

より高価なPCB材料

エラー訂正の必要性の増加(FLITエンコーディング)

Gen6 が一般消費者向け PC に搭載されるまでには時間がかかるかもしれませんが、まずはエンタープライズ サーバーとデータ センターが採用し、次世代の GPU と SSD への道を切り開きます。

PCビルダーのための実践的なヒント

レーン共有を確認する: マザーボードを購入する前に、どの M.2 スロットまたは PCIe スロットが GPU とレーンを共有しているかを確認します。

重要なデバイスには CPU レーンを使用します。GPU とメインの NVMe ドライブは常に CPU ダイレクト レーンを占有する必要があります。

Gen5 に(まだ)執着する必要はありません。ワークロードが I/O に大きく依存しない限り、Gen4 は十分な帯域幅を提供します。

将来に備えるために賢く: Gen4 と Gen5 の両方をサポートするマザーボードを選択すると、今後何年にもわたる互換性が保証されます。

冷却と帯域幅のバランスをとる: 高速 PCIe デバイスは余分な熱を発生するため、良好な空気の流れとヒートシンクが不可欠です。

結論

PCIeレーンはPCの循環システムです。目に見えないながらも、非常に重要な役割を果たします。CPUがいくつのレーンを提供し、どのように割り当てられているかを理解することで、バランスの取れたビルドと、隠れたボトルネックだらけのビルドの違いが生まれます。

PCIe Gen5 が主流になり、Gen6 が間もなく登場するにつれ、これらのレーンの仕組みを理解することで、ゲーミングパワーハウス、クリエイティブワークステーション、高速ストレージサーバーなどを構築する場合でも、よりスマートなハードウェア決定を行うことができます。